集成電路制造工藝與可制造性設計 提升芯片設計成功率的關鍵

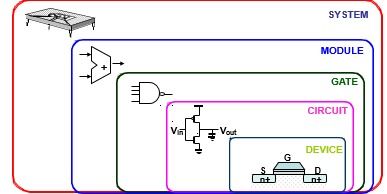

隨著半導體技術的飛速發展,集成電路的設計與制造日益復雜。在這一背景下,可制造性設計(Design for Manufacturing, DFM)成為連接設計與制造的關鍵橋梁,它旨在確保集成電路設計在制造過程中的可行性和高效率。

集成電路制造工藝是半導體產業的核心,通常包括晶圓準備、薄膜沉積、光刻、蝕刻、離子注入、化學機械拋光等多個步驟。現代工藝已進入納米尺度,如7nm、5nm甚至更先進的制程,這對工藝控制和缺陷管理提出了極高要求。純粹追求工藝先進性往往面臨良率挑戰,這正是可制造性設計發揮作用的地方。

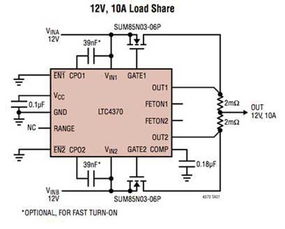

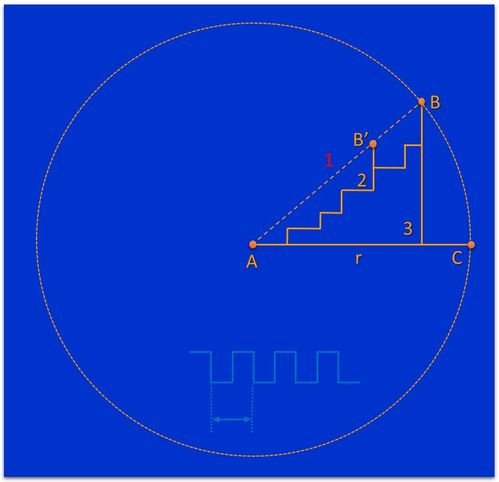

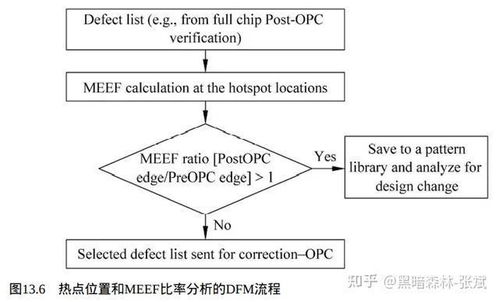

可制造性設計是一種系統性的方法,它在集成電路設計階段就考慮制造工藝的局限性,通過優化設計規則、布局和材料選擇,來減少制造缺陷、提高產品良率并縮短上市時間。具體而言,DFM涉及多個方面:它強調對工藝變化的容忍度,例如通過添加冗余結構或使用統計模型來補償光刻和蝕刻過程中的偏差;它關注熱點檢測與消除,利用EDA工具識別可能導致短路或開路的布局區域;DFM還包括測試與封裝友好設計,確保芯片在制造后易于測試和封裝。

在實際應用中,DFM與集成電路設計流程緊密集成。設計師需要使用先進的仿真工具,結合制造廠提供的工藝設計套件,進行多次迭代優化。例如,在物理設計階段,通過DFM規則檢查布局是否符合制造要求;在邏輯設計階段,考慮晶體管尺寸和互連線的可制造性。這不僅降低了制造成本,還顯著提升了芯片的可靠性和性能。

集成電路制造工藝與可制造性設計的結合是推動半導體行業進步的重要動力。隨著人工智能、物聯網等新興應用的興起,對高性能、低功耗芯片的需求將持續增長,DFM將更顯關鍵。未來,隨著工藝節點進一步縮小,DFM技術將不斷演進,集成更多智能算法和實時數據,助力設計團隊在競爭激烈的市場中脫穎而出。

如若轉載,請注明出處:http://www.aozhang.cn/product/31.html

更新時間:2026-01-06 16:15:57